The following article explains the theory of operation of an ideal diode circuit implemented using a p-channel MOSFET and a matched PNP transistor pair. Typical applications for the ideal diode are devices such as solar chargers, where power efficiency is of a great importance.

Table of Contents

Introduction

Diodes are devices that allow the electric current to flow in only one direction. As shown in the image below, the current is allowed to flow from the anode towards the cathode but not the other way around.

Diodes have many applications ranging from simple reverse polarity protection to full bridge rectifiers. There is plenty of available material explaining the diode basics, therefore I would like to skip this part and only cover one particular aspect of diodes which makes them rather power inefficient devices. This article shall cover the forward voltage drop denoted in the datasheet as ![]() .

.

![]() is the voltage measured between the anode and the cathode of a diode subjected to an electric current

is the voltage measured between the anode and the cathode of a diode subjected to an electric current ![]() in its forward direction. Whereas the anode corresponds to the positive side and the cathode to the negative. Typical values of

in its forward direction. Whereas the anode corresponds to the positive side and the cathode to the negative. Typical values of ![]() are 0.6 Volts for a standard silicone Diode and as low as 0.1 Volts for a Schottky type diode. The value of

are 0.6 Volts for a standard silicone Diode and as low as 0.1 Volts for a Schottky type diode. The value of ![]() is a function of the forward bias current

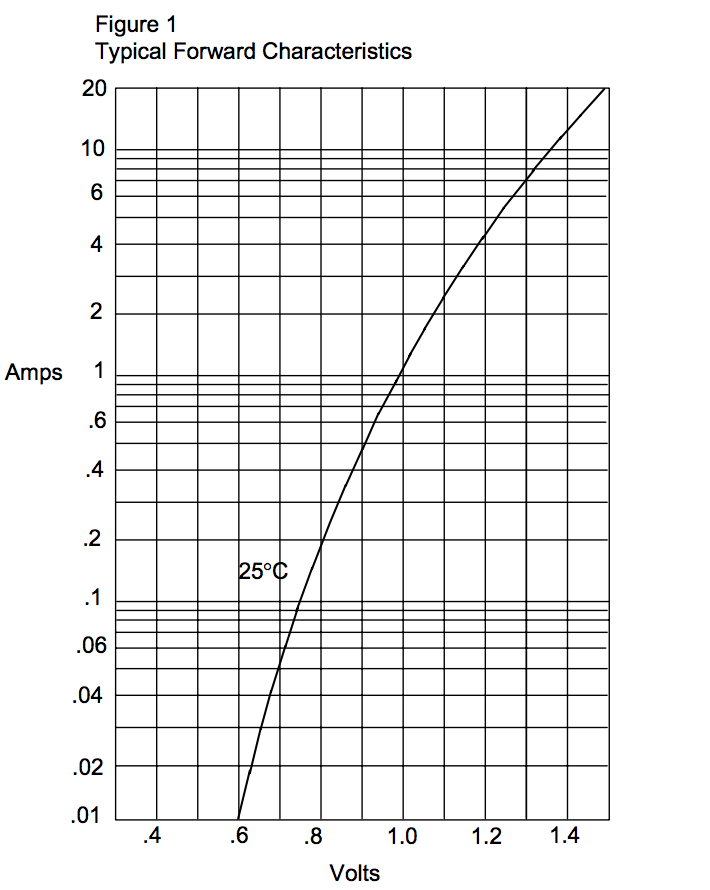

is a function of the forward bias current ![]() as shown in the diagram below.

as shown in the diagram below.

The above diagram plots the forward voltage drop ![]() (horizontal axis) versus the forward bias current

(horizontal axis) versus the forward bias current ![]() (vertical axis) for a 1N4007 or similar diode. As one can see,

(vertical axis) for a 1N4007 or similar diode. As one can see, ![]() can go as high as 1 Volt for 1 Ampere of current, which results in a dissipated power loss of 1 Watt.

can go as high as 1 Volt for 1 Ampere of current, which results in a dissipated power loss of 1 Watt.

As the name of this article suggests, the ideal diode is one which exhibits no (or very little) power loss. Thus, it should have ![]() (or close to) for a wide range of

(or close to) for a wide range of ![]() . Presented in this article is a small circuit that mimics the behavior of of a diode with a near zero forward voltage drop.

. Presented in this article is a small circuit that mimics the behavior of of a diode with a near zero forward voltage drop.

Circuit Diagram

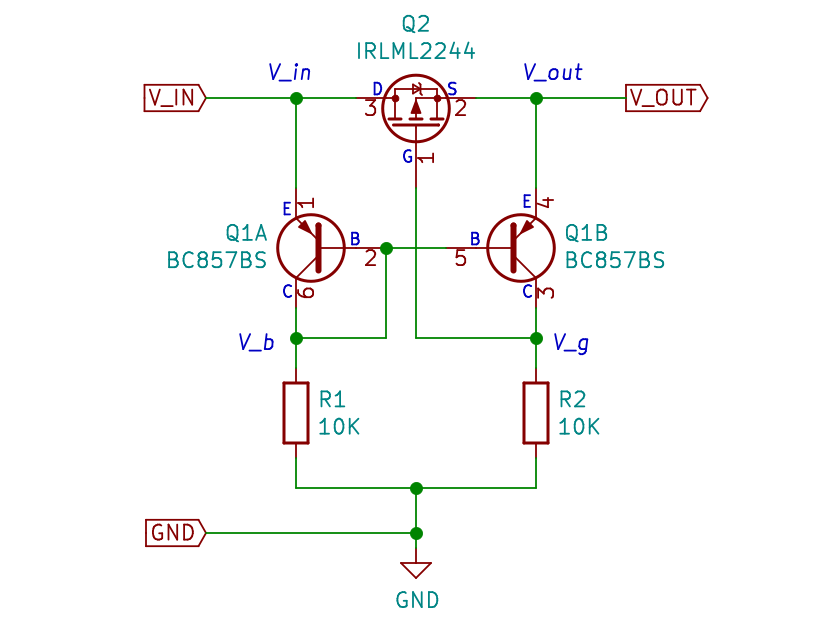

As seen in the schematic below, the ideal diode consists of a p-channel MOSFET Q2 and a voltage comparator consisting of a matched PNP transistor pair Q1A and Q1B.

MOSFET

The IRLML2244 p-channel MOSFET Q2 is driven in the reverse direction, whereas its drain pin 3 is connected to the input voltage ![]() and its source pin 2 provides the output voltage

and its source pin 2 provides the output voltage ![]() . This ensures that the MOSFET’s intrinsic diode is aligned in the direction of forward current flow and prevents any reverse current from flowing through it.

. This ensures that the MOSFET’s intrinsic diode is aligned in the direction of forward current flow and prevents any reverse current from flowing through it.

This MOSFET exhibits a very low static drain-to-source on-resistance ![]() at a gate-source voltage of

at a gate-source voltage of ![]() and a drain current of

and a drain current of ![]() (see datasheet). The resulting measured forward voltage drop amounts to

(see datasheet). The resulting measured forward voltage drop amounts to ![]() at

at ![]() .

.

Voltage Comparator

A voltage comparator circuit has been implemented around the PNP transistors Q1A and Q1B. It is important that these transistors have identical characteristics, otherwise the comparator will not have the required precision. Thus, these transistors part of a BC857BS matched transistor pair sharing the same package. Having both transistors inside one physical package ensures that they are thermally coupled and avoids diverging characteristics due to different junction temperatures.

The voltage comparator compares the voltages ![]() to

to ![]() and controls the MOSFET gate voltage

and controls the MOSFET gate voltage ![]() across the resistor R2.

across the resistor R2.

The following equations apply for the voltage ![]() between the transistor’s base and the power supply ground:

between the transistor’s base and the power supply ground:

![]()

![]()

where ![]() and

and ![]() are the emitter-base voltages of transistors Q1A and Q1B. And:

are the emitter-base voltages of transistors Q1A and Q1B. And:

![]()

![]()

Where ![]() is the specified base-emitter voltage drop for BC857BS (see datasheet). Due to the properties of the base-emitter junction which is essentially a diode, the voltages

is the specified base-emitter voltage drop for BC857BS (see datasheet). Due to the properties of the base-emitter junction which is essentially a diode, the voltages ![]() and

and ![]() are clamped to

are clamped to ![]() . A current can only flow through the emitter-base junction of Q1A or Q1B if the corresponding emitter-base voltage

. A current can only flow through the emitter-base junction of Q1A or Q1B if the corresponding emitter-base voltage ![]() or

or ![]() reaches (gets slightly higher than)

reaches (gets slightly higher than) ![]() .

.

Forward Bias

The following holds true when the ideal diode is forward biased:

![]()

![]()

The larger of ![]() and

and ![]() will be clamped to

will be clamped to ![]() which leads to the following statements:

which leads to the following statements:

![]()

![]()

Consequently, current will flow through the emitter-collector path of transistor Q1A while no current will flow through the emitter-collector path of Q1B. Thus, the voltage ![]() across the resistor R2 will be equal (or near equal) to 0V. This will lead to a negative gate-source voltage

across the resistor R2 will be equal (or near equal) to 0V. This will lead to a negative gate-source voltage ![]() and cause the MOSFET Q1B to turn on.

and cause the MOSFET Q1B to turn on.

Reverse Bias

The following holds true when the ideal diode is reverse biased:

![]()

![]()

The larger of ![]() and

and ![]() will be clamped to

will be clamped to ![]() which leads to the following statements:

which leads to the following statements:

![]()

![]()

Consequently, current will flow through the emitter-collector path of transistor Q1B while no current will flow through the emitter-collector path of Q1A. Thus, the voltage ![]() across the resistor R2 will be equal (or near equal) to

across the resistor R2 will be equal (or near equal) to ![]() . This will lead to near zero gate-source voltage

. This will lead to near zero gate-source voltage ![]() and cause the MOSFET Q1B to turn off.

and cause the MOSFET Q1B to turn off.

PCB Layout

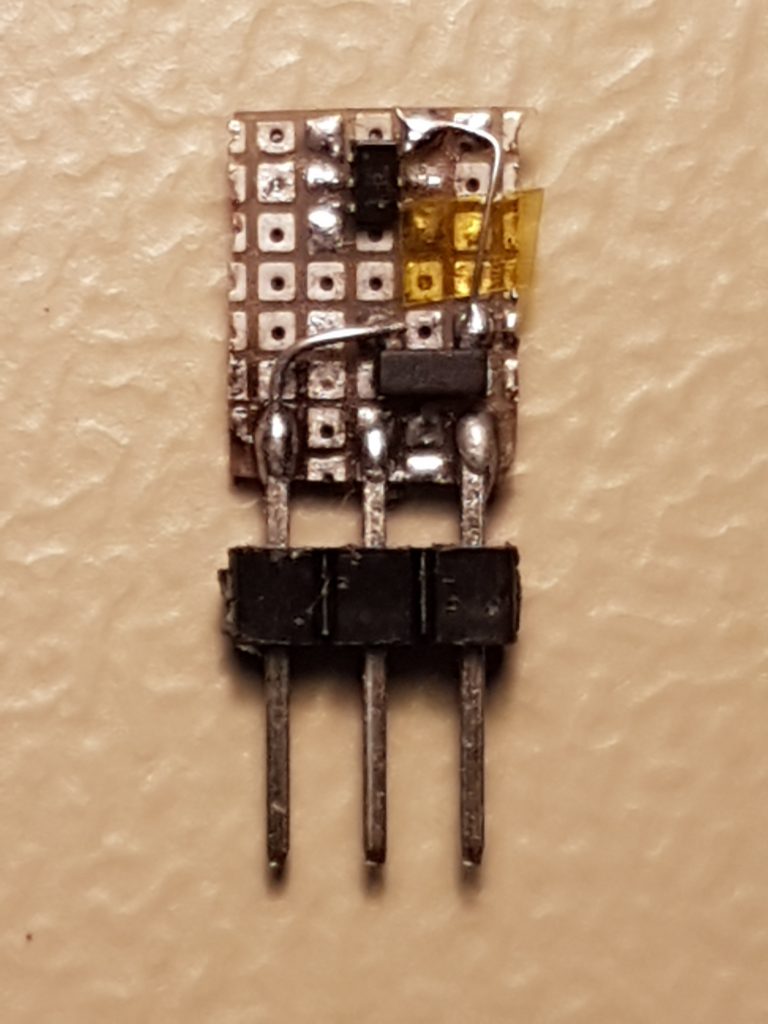

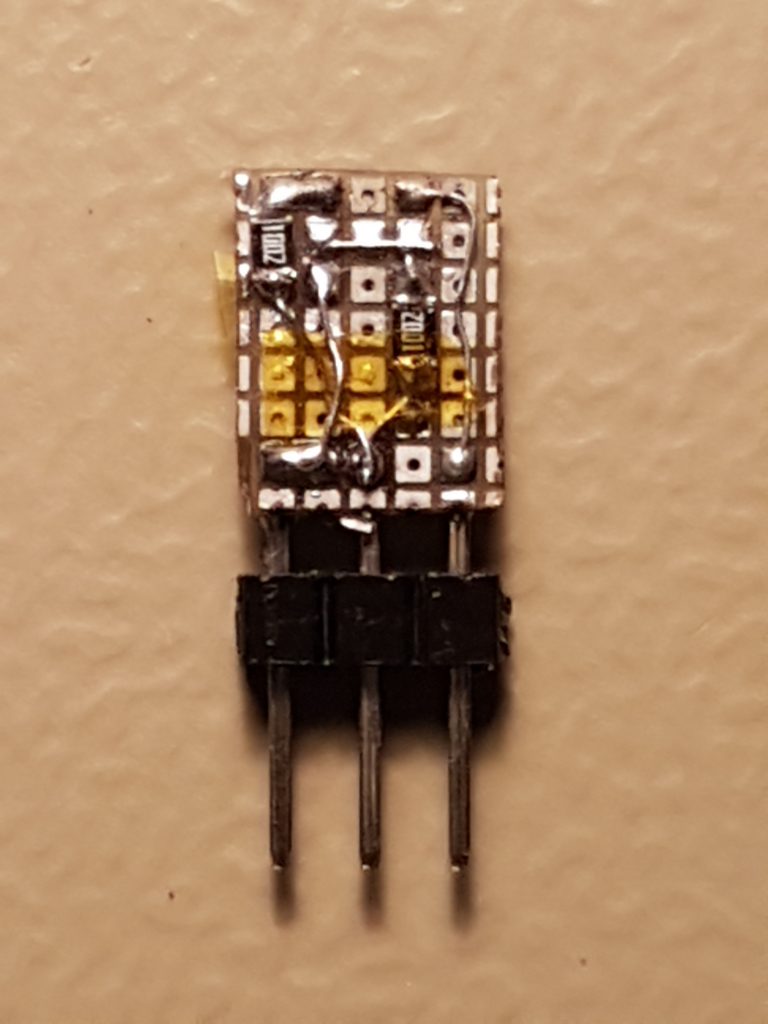

The circuit has been implemented on a SMD prototyping board as shown in the pictures below. The surface mount MOSFET, transistor pair and 0805 resistors have been connected using jumper wires. The three terminals of the ideal diode have been connected to a pin header.

The left picture shows the top side of the PCB with the visible MOSFET (3 pin package) and dual transistor (6 pin package). The right picture shows the backside of the PCB with the two 0805 resistors. Note that the pads on both sides are connected through the holes.

Following are the pin assignments on the pin header, assuming pin 1 is the leftmost pin and pin 3 is the rightmost pin on the left picture:

- Pin 1:

- Pin 2: GND

- Pin 3:

Bill of Material

Following is the list of parts required for building the ideal diode. Please consider supporting this website by purchasing your the required parts using the affiliate links below:

- IRLML2244 logic level p-channel MOSFET

- BC857BS PNP transistor pair

- 10KΩ 0805 SMD resistors

- 2.54mm pin header

- SMD prototyping board

Update (April 19, 2021)

David Albert has kindly provided the following feedback to this design. With his permission, I hereby quote his emails and diagrams he has provided.

Feedback on April 14, 2021

Hi Karim,

I found your ideal diode circuit on your blog (https://www.microfarad.de/blog/the-ideal-diode/); thanks for sharing it; it’s a clever design! I simulated it in LTSpice and it appeared to work, so I designed it into a circuit as an ideal diode replacement for ORing USB power with a 6-7V battery.

Unfortunately, I found that whenever I connected the battery, the USB port experienced a surge and would shut down. I went back to the simulation and I think I see the problem; if you agree, I think it would be good to note it on your blog so others don’t have the same problem. I’m still thinking about how to fix it and will let you know if I come up with an elegant solution (please let me know if you come up with one too).

The problem is that the MOSFET requires a finite amount of time to turn off. When the battery (V2 in my circuit) turns on, the BE junction of Q2 is forward biased and current flows through it and R2, causing a larger current flow through the emitter to collector (as your circuit intends); this works as designed. This current through Q2 is what charges M1’s gate causing it to turn off. Unfortunately, the BC857BS has a maximum current of 200mA and that charges the MOSFET gate slowly (high-current MOSFET drivers exist for exactly this reason: to charge/discharge gate capacitance quickly).

During the time Q2 is charging M1’s gate, M1 remains on and creates a short circuit between the two power sources and a *lot* of current will flow. This caused the protection circuitry on my USB port to kick in and shut down the port, but it could do much worse if such protection circuitry is not present.

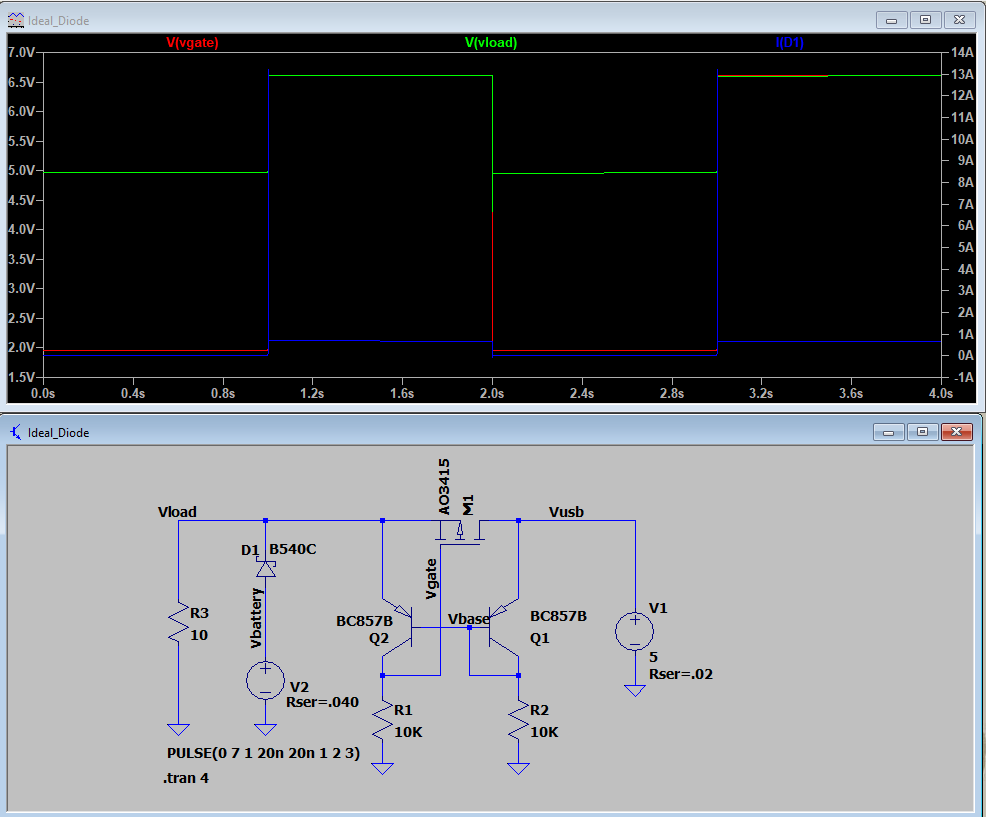

The LTSpice simulation actually shows this problem (I just wasn’t sharp enough to look for it when I simulated it initially). The blue trace below shows the current through D1 (output of battery). Notice how the current surges momentarily above 13A. You can reduce the size of the surge (and the power consumption of the circuit) by increasing R1. You can reduce the surge a little more (at the expense of wasted power) by reducing R2, but the underlying problem remains: there is a brief period when the supplies are short circuited.

I’ve attached the LTSpice simulation in case you want to try it yourself…if you have any ideas for an elegant fix, I’d be grateful if you’d share them.

Thanks and regards,

Dave Albert

Follow-up on April 14, 2021

Hi Karim,

You are welcome to post the explanation and thank you for looking at it and responding so quickly!

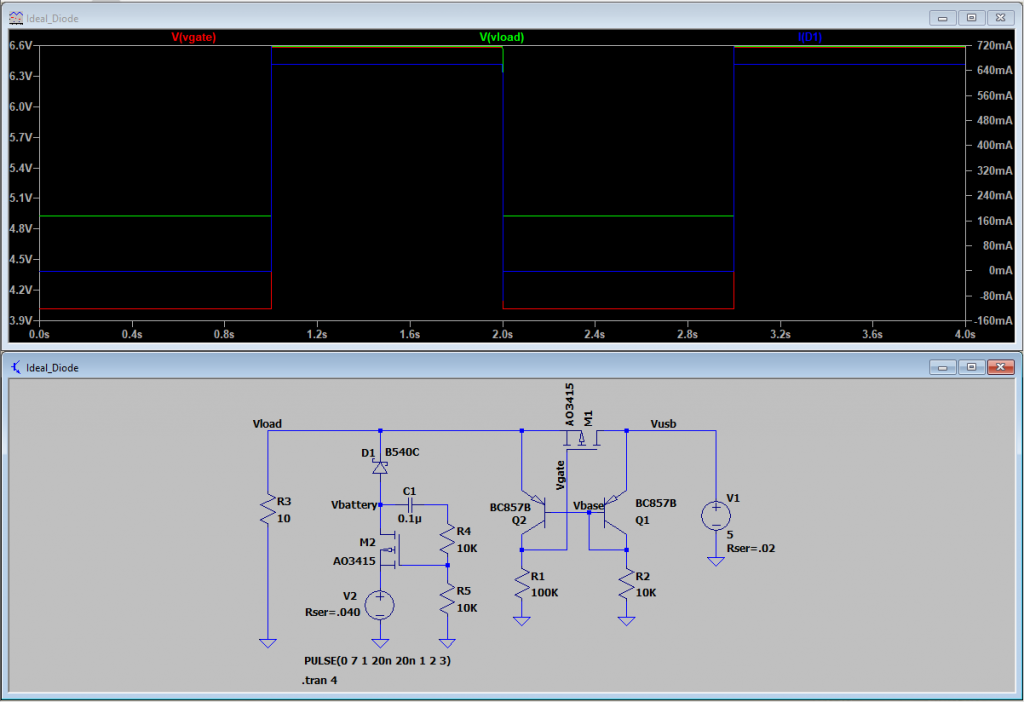

I slept on it and adding a soft-start circuit to the higher voltage source seems likely to solve the issue (and is probably a good idea anyway to reduce capacitor inrush currents). I simulated it below; the values shown below were not carefully chosen; I’ll tweak them later and then test it, but the simulation seems to work without the large reverse currents. If you have any better ideas, please let me know.

Best regards,

David

Hi Karim,

I found your ideal diode circuit on your blog (https://www.microfarad.de/blog/the-ideal-diode/); thanks for sharing it; it’s a clever design! I simulated it in LTSpice and it appeared to work, so I designed it into a circuit as an ideal diode replacement for ORing USB power with a 6-7V battery.

Unfortunately, I found that whenever I connected the battery, the USB port experienced a surge and would shut down. I went back to the simulation and I think I see the problem; if you agree, I think it would be good to note it on your blog so others don’t have the same problem. I’m still thinking about how to fix it and will let you know if I come up with an elegant solution (please let me know if you come up with one too).

The problem is that the MOSFET requires a finite amount of time to turn off. When the battery (V2 in my circuit) turns on, the BE junction of Q2 is forward biased and current flows through it and R2, causing a larger current flow through the emitter to collector (as your circuit intends); this works as designed. This current through Q2 is what charges M1’s gate causing it to turn off. Unfortunately, the BC857BS has a maximum current of 200mA and that charges the MOSFET gate slowly (high-current MOSFET drivers exist for exactly this reason: to charge/discharge gate capacitance quickly).

During the time Q2 is charging M1’s gate, M1 remains on and creates a short circuit between the two power sources and a *lot* of current will flow. This caused the protection circuitry on my USB port to kick in and shut down the port, but it could do much worse if such protection circuitry is not present.

The LTSpice simulation actually shows this problem (I just wasn’t sharp enough to look for it when I simulated it initially). The blue trace below shows the current through D1 (output of battery). Notice how the current surges momentarily above 13A. You can reduce the size of the surge (and the power consumption of the circuit) by increasing R1. You can reduce the surge a little more (at the expense of wasted power) by reducing R2, but the underlying problem remains: there is a brief period when the supplies are short circuited.

I’ve attached the LTSpice simulation in case you want to try it yourself…if you have any ideas for an elegant fix, I’d be grateful if you’d share them.

Thanks and regards,

Dave Albert

Hi David,

many thanks for the elaborate problem description. Honestly, I’ve never thought this far while implementing the circuit. It is based on a common design found on the web. So I have built it and written down the description, as well as my explanation on how it works. I agree that the transient current peak can be a potential issue for applications that do not tolerate a brief current peak in the backward direction. If you don’t mind, is it ok if I publish the text you have just sent me, with minor modifications perhaps? As I believe that I couldn’t explain it any better.

Best regards,

Karim

Hi Karim,

You are welcome to post the explanation and thank you for looking at it and responding so quickly!

I slept on it and adding a soft-start circuit to the higher voltage source seems likely to solve the issue (and is probably a good idea anyway to reduce capacitor inrush currents). I simulated it below; the values shown below were not carefully chosen; I’ll tweak them later and then test it, but the simulation seems to work without the large reverse currents. If you have any better ideas, please let me know.

Best regards,

David